# Datenverarbeitungssysteme

## Technische Informatik Sommersemester 2016

Prof. Dr. Wolfgang Mauerer wolfgang.mauerer@oth-regensburg.de

## Inhalt

#### Überblick und Einführung

Literatur Lernziele

#### Datenrepräsentation und -manipulation

Zahlendarstellung Endianess Zeichendarstellung Gleitkommazahlen Bitoperationen

#### Prozessorarchitektur

Grundkoperationen einer CPU von Neumann- und Harvard-Architektur Grundkonzept der Befehlsausführung Befehlszyklen und Pipelines Optimierungsmechanismen Sonstige Themen

#### Hochsprachen und Assembler I

Instruktionssets Die Werkzeugkette ARM-Assembler ARM-Assembler Befchisgruppen Speicheraufbau Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken Bibliotheken die Aufgaben und Überblick Syntaxanalyse Semantische Analyse & Codegenerierung Optimierungen

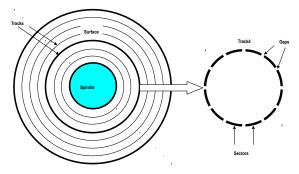

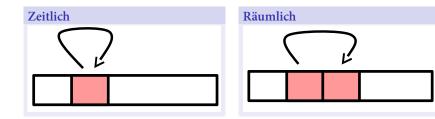

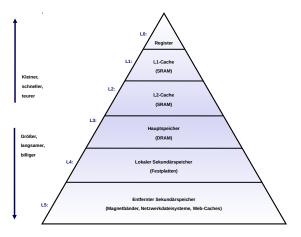

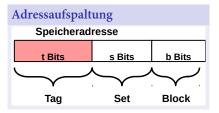

#### Speicherhierarchie, Caches und MMUs

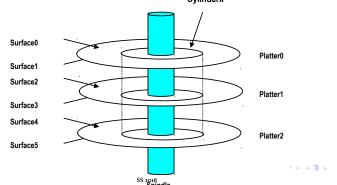

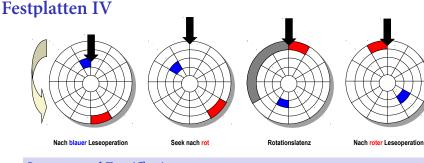

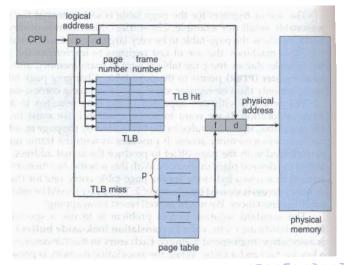

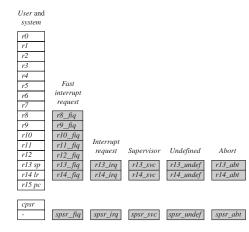

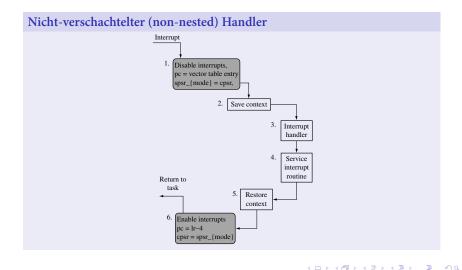

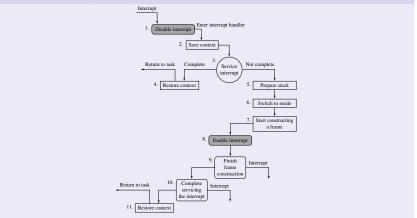

RAM-Speicher Festplatten und Massenspeichergeräte CPU-Speicher-Kluft und Lokalität Caches Caches-Optimierungen Virtueller Speicher und Memory Management Units

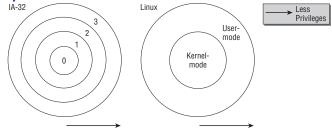

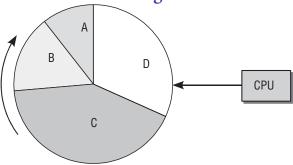

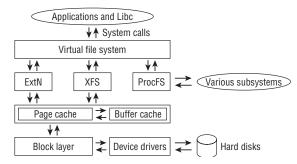

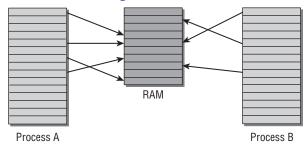

#### Betriebssysteme

Grundstruktur Memory Management Unit und Adressrauwnerwaltung Interrupts Ausprägungen von BS Fallbeispiel: Linux Blockgeräte und Dateisysteme

## Dozent

### **OTH Regensburg**

- Professor f

ür theoretische Informatik

- Forschungsinteressen

- Innovation durch Theorie (Zufallserzeugung, stochastische Methoden)

- Industrie 4.0 (Cyber Physical und Smart Embedded)

- Statistik und maschinelles Lernen in der SW-Entwicklung

- Hacken und Beweisen

#### Siemens Corporate Research

- Linux (Kernel, Low-Level)

- Harte Echtzeit (MRT, Simatic, Àndroit, ...)

- Statistik und maschinelles Lernen in der SW-Architektur siemens.github.com/ codeface

イロト イポト イヨト イヨト 二日

Früher: MPL (QIT, QED)

## Scheinkriterien/Übungen

#### Scheinkriterien

- Klausur (90min) am Ende des Semesters

- Keine Hilfsmittel

- Material der gesamten Vorlesung relevant (orientiert sich an Übungsaufgaben).

### Übungen

- Gruppe 1: Fr, 11:45-13:15, U514 (Herr Kölbl)

- Gruppe 2: Fr, 11:45-13:15, U521 (Herr Welker)

- Gruppe 3: Fr, 13:30-15:00, U514 (Herr Kölbl)

イロト 不得 トイラト イラト 一日

## Aufwand

- ▶ 4 SWS Vorlesung, 2 SWS Übungen

- ▶  $\approx$  90h Vorlesung und Übungen,  $\approx$  150h Eigenstudium

イロト イポト イモト イモト 一日

## Informationsquellen

#### Informationsquellen

- Angegebene Literatur

- Herstellerdokumentation von ARM

- Weitere im G.R.I.P.S. verlinkte Dokumente

### **Technische Details**

- ...werden/können nicht vollständig in der Vorlesung abgehandelt werden

- Eigeninitiative!

- Notwendige Fähigkeit für industrielle Tätigkeiten

イロト イポト イラト イラト 一日

## Literatur

R. E. Bryant und D. O'Hallaron, Computer Systems, 2ed, Pearson, 2010.

A. N. Sloss, D. Symes, C. Wright, ARM System Developer's Guide, Morgan Kaufmann, 2004.

W. Mauerer, Professional Linux Kernel Architecture, Wiley/Wrox, 2009.

## Lernziele

- Struktur von Datenverarbeitungssystemen

- Funktionsweise und Implementierung von CPUs

- Ganzzahl- und Gleitkommazahldarstellung und -arithmetik

- Assemblerprogrammierung (32-Bit ARM)

- Speicherhierarchie; RAM und Caches

- Massenspeichergeräte

- Arbeitsweise von Compilern, Bindern und Ladern

- Grundlagen von Betriebssystemen

- Grundlagen von Netzwerken

### Spezialvorlesungen

- Ziel: Technik-Stapel verstehen!

- Vertiefung und Details: Spezialvorlesungen

## **DV-Systeme: Theorie und Praxis**

#### Theorie

- Abtraktes Maschinenmodell

- Details bewusst ignoriert/abwesend

- Modellbildung

#### **Reale Systeme**

- Nicht das Gegenteil der Theorie

- Abstraktion nicht immer möglich

- Einzelschichten einfach bis trivial, Kombination hochkomplex

(日)

### **Bugs und Optimierungen**

- Häufig querschneidend

- Verständnis Gesamtsystem (nicht: ausschalten-einschalten)

## Reale Welt I

- Low-Level-Software, Gerätetreiber etc.: Entkopplung von HW unmöglich

- Konstanten und Faktoren in asypmtotischer Notation: Praktische Umsetzbarkeit

- ▶ Effizienz: 50 Cent weniger bei 10<sup>6</sup> Geräten ☞ Substantieller Unterschied

- Random Access Memory: Unrealistische Annahme

## Reale Welt II

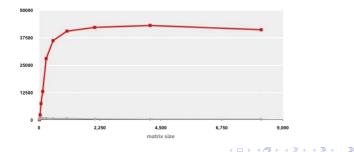

### Algorithmus und Implementierung

- Optimaler Algorithmus bedeutet nicht optimale Leistung!

- Implementierung ist entscheidender Faktor

- Systemeigenschaften müssen genutzt werden

## Reale Welt III

#### Computer kommunizieren

- Ein- und Ausgabe theoretisch häufig »wegabstrahierbar«

- Praktisch: Zahlreiche Sonderfälle

- Interne und externe Kommunikation

- Zuverlässigkeit und Leistung

- (Teilweise) defekte Medien

- Performance: Vielschichtiges Zusammenspiel

イロト イポト イラト イラト 一日

## Lernziel II

#### Zerlegen statt neu bauen

- Seltene Fälle

- Neue CPU entwerfen

- Neue Busarchitektur entwerfen

- Neues Betriebssystem schreiben

- Neues Kommunikationsprotokoll entwerfen

- Assembler schreiben

- Häufige (industrielle) Fälle

- Riesige Mengen an Code verstehen

- Betriebssysteme erweitern

- CPUs »bis zum letzten Bit« ausnutzen

- Assembler lesen

- Systemumspannende Software verstehen und erweitern

- Hacken: Kreative und technisch tiefe Operationen am System

- Hacken ≠ Cracken!

イロト イポト イヨト イヨト

## Hardware/BYOD

### Zielarchitektur

- ARM-Prozessoren: Raspberry Pi

- ...zahllose Handys und Tablets

- Typischer Embedded-Prozessor

- Marktanteil typischer Desktop-Prozessoren (x86) verschwindend gering

#### Plattformen

- Physikalischer Raspberry Pi

- Virtueller rpi (auf qemu-Basis)

CIP-Pool

- Eigenes Gerät: Android/Cyanogenmod (eigene Verantwortung!)

イロト イポト イヨト イヨト

Datenrepräsentation und -manipulation

## Inhalt

#### Überblick und Einführung

Literatur Lernziele

#### Datenrepräsentation und -manipulation

Zahlendarstellung Endianess Zeichendarstellung Gleitkommazahlen Bitoperationen

#### Prozessorarchitektur

Grundoperationen einer CPU von Neumann- und Harvard-Architektur Grundkonzept der Befehlsausführung Befehlszyklen und Pipelines Optimierungsmechanismen Sonstige Themen

#### Hochsprachen und Assembler I

Instruktionssets Die Werkzeugkette ARM-Assembler ARM-Assembler programmierung Befehlsgruppen Speicheraufbau Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken dur die Behlick Syntaxanalyse Semantische Analyse & Codegenerierung Optimierungen

#### Speicherhierarchie, Caches und MMUs

RAM-Speicher Festplatten und Massenspeichergeräte CPU-Speicher-Kluft und Lokalität Caches Caches-Optimierungen Virtueller Speicher und Memory Management Units

#### Betriebssysteme

Grundstruktur Memory Management Unit und Adressrauwnerwaltung Interrupts Ausprägungen von BS Fallbeispiel: Linux Blockgeräte und Dateisysteme

## Zahlenkodierung I

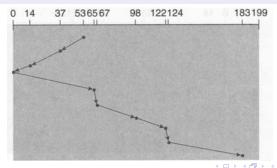

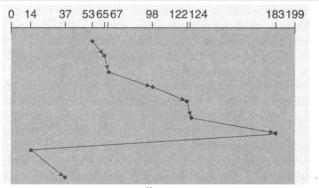

Abbildung basiert auf Bryant & O'Hallaron

・ロト ・ 聞 ト ・ 臣 ト ・ 臣 ト

## Datenrepräsentation und -manipulation

#### Informationskodierung Zahlendarstellung Speicheraufteilung in Blöcke: Io Finger: Dezimalsystem (10) Ziffern) Bytes (8 Bits), Words (16/32/64 Bits) Computer: Systematischer Zugriffe auf Speicher erfolgt Elektrisches Signal (ein/aus, immer in Byte- oder größeren geladen/nicht geladen, ...) Schritten (bis auf pathologische 2 Zustände als Basis: Bit (0/1) Ausnahmen, bsp. TI Bitfolgen zur Kodierung von TMS34010) Zahlen, Zeichen, Bildern, ... Folge von Bits: Natürliche Zahl

$x \in \mathbb{N}$

Interpretation nach Stellenwertsystem

## Zahlenkodierung II

Dezimalsystem: Basis b = 10

$$1026_{10} = 1 \cdot 1000 + 0 \cdot 100 + 2 \cdot 10 + 6 \cdot 1$$

= 1 \cdot 10^3 + 0 \cdot 10^2 + 2 \cdot 10^1 + 6 \cdot 10^0

=  $\sum_{i=0}^{N} x_{(i)} \cdot 10^i$

► Binärsystem: Basis *b* = 2.

$$10110_{2} = 1 \cdot 2^{4} + 0 \cdot 2^{3} + 1 \cdot 2^{2} + 1 \cdot 2^{1} + 0 \cdot 2^{0}$$

$$= 1 \cdot 16 + 0 \cdot 8 + 1 \cdot 4 + 1 \cdot 2 + 0 \cdot 1$$

$$= \sum_{i=0}^{N} x_{(i)} \cdot 2^{i}$$

$$= 22_{10}$$

(日)

## Zahlenkodierung III

### Kodierung

- Gebräuchliche Basen: 2 (Binär), 8 (Oktal), 10 (Dezimal), 16 (Hexadezimal)

- Jedes x ∈ N ist in jeder Basis eineindeutig darstellbar (ggf. Nullen von links entfernen: 00101<sub>2</sub> = 101<sub>2</sub>). Voraussetzung: Unendlich viele Bits verfügbar.

#### Hexadezimalzahlen

- Basis b = 16: 10 Ziffernsymbole nicht ausreichend

- Erweiterung: Buchstaben als zusätzliche Ziffernsymbole

- $A_{16} \equiv 10_{10}, B_{16} = 11_{10}, ..., F_{16} = 15_{10}.$

- Einzelne Ziffer deckt vier Bits ab. Kompakte Schreibweise für Kombinationen mehrerer Bytes

イロト イポト イヨト イヨト 二日

Datenverarbeitungssysteme

## Zahlenkodierung IV

### Beispiel

$$BEEF_{16} = B \cdot 16^3 + E \cdot 16^2 + E \cdot 16^1 + F \cdot 16^0$$

= 11 \cdot 16^3 + 14 \cdot 16^2 + 14 \cdot 16^1 + 15 \cdot 16^0

= 48897\_{10}

(日)

## Rechnen mit Binärzahlen I

#### Addition

- ▶ Binär: 0 + 0 = 0, 0 + 1 = 1 + 0 = 1, 1 + 1 = 10

- Stellenweise Addition mit Übertrag (Beispiel: Siehe Tafel)

- Problem: Endliche Bit-Anzahl. Beispiel 4 Bits: 1000<sub>2</sub> + 1000<sub>2</sub> = 10000<sub>2</sub> wird auf 0000<sub>2</sub> »gestutzt«.

- Überlauf!

#### speed.c

```

uint8_t speed = 240;

for (uint8_t i = 0; i < 30;

i++) {

// Beschleunigen

speed += 1;

printf("Auto faehrt mit

%u km/h\n", speed);

```

イロト イポト イヨト イヨト 二日

## Rechnen mit Binärzahlen II

#### Probleme

- Begrenzter Wertebereich. Maximale Größen der verwendeten Daten sind essentiell!

- Subtraktion: Wie negative Resultate repräsentieren?

- ▶ Division: Resultat nicht notwendigerweise  $\in \mathbb{N}$ .

#### **Multiplikation**

Schulverfahren – siehe Tafel.

イロト イポト イヨト イヨト 二日

## Zahlendarstellung I: Zweierkomplement

#### Negative Ganzzahlen repräsentieren

Naïv (bzw. Sign-Magnitude): Höchstes Bit als Vorzeichen verwenden (0 = "+", 1 = "-"):

> 1101 = -50101 = +5

- Problem: Zwei Kodierungen f

ür die Zahl o.

- ▶ 1000<sub>2</sub> = −0

- ▶ 0000<sub>2</sub> = +0

- ▶ Mathematisch: +0 = −0. ☞ Bitverschwendung!

イロト イポト イヨト イヨト ニヨー

## Zahlendarstellung II: Zweierkomplement

### Zweierkomplementdarstellung

- Höchstwertiges Bit wird mit negativem Gewicht interpretiert

- Sei  $\vec{x}$  eine Folge von 8 Bits (als Vektor interpretiert):

- Ganzzahliger Wert:  $b2u_8(\vec{x}) = \sum_{i=0}^7 x_i 2^i$

- Zweierkomplement:  $b2t_8(\vec{x}) = \sum_{i=0}^{6} x_i 2^i x_7 2^7$

- ▶ Jede darstellbare Zahl  $x \in [-2^7, 2^7 1]$  eineindeutig (bijektiv) identifiziert

- Achtung: Asymmetrisches Intervall

(日)

## Zahlendarstellung II

#### Zweierkomplement bei 8 Bits

| Binär    | Zweierkomplement | Vorzeichenlos |

|----------|------------------|---------------|

| 00000000 | 0                | 0             |

| 0000001  | 1                | 1             |

|          |                  |               |

| 01111110 | 126              | 126           |

| 01111111 | 127              | 127           |

| 10000000 | -128             | 128           |

| 10000001 | -127             | 129           |

| 10000010 | -126             | 130           |

|          |                  |               |

| 11111110 | -2               | 254           |

| 11111111 | -1               | 255           |

### Wert des Speicherinhalts ist immer interpretationsabhängig!

イロト イポト イモト イモト 一日

## Zahlendarstellung III

Zweierkomplement - allgemein

► Formal:

$$b2t_w : \mathbb{F}_2^w \to \mathbb{Z}$$

$$b2t_w(\vec{x}) = \sum_{i=0}^{w-2} x_i 2^i - x_{w-1} 2^{w-1}$$

- Umkehrung:  $t2b_w : \mathbb{Z} \to \mathbb{F}_2^w$  mit  $t2b = b2t^{-1}$

- Wohldefiniert, da b2t bijektiv

(日)

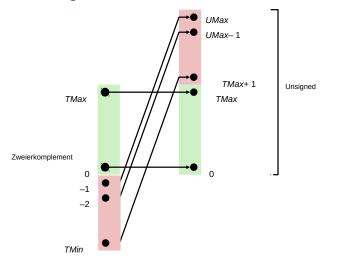

## Zahlendarstellung IV

### Typumwandlung

- Positive Werte: Gleiches Bitmuster

- Allgemein

- Signed  $\rightarrow$  Unsigned:  $t2u_w(x) \equiv b2u_w(t2b_w(x))$

- ▶ Unsigned  $\rightarrow$  Signed:  $u2t_w(x) \equiv b2t_w(u2b_w(x))$

- Bitmuster beibehalten, Inhalt neu interpretieren

- CPUs verwenden üblicherweise gleiche Elementarinstruktionen für signed und unsigned-Arithmetik

イロト イポト イラト イラト 一日

Datenverarbeitungssysteme Datenrepräsentation und -manipulation Zahlendarstellung

## Zahlendarstellung V

Abbildung basiert auf Bryant & O'Hallaron

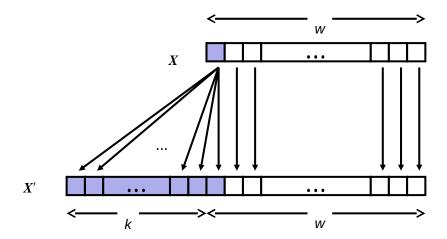

## Sign Extension I

#### Aufgabe

- ▶ Gegeben: Vorzeichenbehaftete *w*-Bit-Ganzzahl

- ▶ Gesucht: Zahl mit *w* + *k* Bits und gleichem numerischen Wert

- Trivial f

ür vorzeichenlose Zahlen!

#### Vorgehensweise

- Vorzeichenbit an k neuen (höchstwertige) Positionen kopieren

- w Bits f

ür Wert

übernehmen

イロト イポト イラト イラト 一日

Datenverarbeitungssysteme Datenrepräsentation und -manipulation Zahlendarstellung

## Sign Extension II

э

・ロト ・ 聞 ト ・ 国 ト ・ 国 ト

## Sign Extension III

### Sign Extension

short int x = 15213; int ix = (int) x; short int y = -15213; int iy = (int) y;

|    | Dezimal | Hexadezimal | Binär                               |

|----|---------|-------------|-------------------------------------|

| x  | 15213   | 3B 6D       | 00111011 01101101                   |

| ix | 15213   | 00 00 3B 6D | 0000000 0000000 00111011 01101101   |

| у  | -15213  | C4 93       | 11000100 10010011                   |

| iy | -15213  | FF FF C4 93 | 11111111 11111111 11000100 10010011 |

Abbildung basiert auf Bryant & O'Hallaron

イロト イポト イヨト 「ヨ」

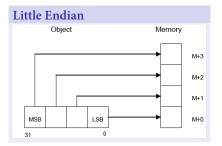

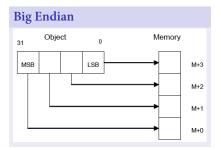

## **Endianess I**

### Mehrere Bytes pro Zahl

- ▶ Betrachte Zahl 0x12345678 im Speicher an Position 0x1000

- ▶ Mehrere Bytes erforderlich  $\Rightarrow$  Unterschiedliche Anordnungen möglich

| Speicheradresse | 0 <i>x</i> 1000 | 0 <i>x</i> 1001 | 0 <i>x</i> 1002 | 0 <i>x</i> 1003 |

|-----------------|-----------------|-----------------|-----------------|-----------------|

| Big Endian      | 12              | 34              | 56              | 78              |

| Little Endian   | 78              | 56              | 34              | 12              |

### Konventionsfrage

- Little Endian: Intel x86, AMD64, ARM (erste Versionen)

- Big Endian: Motorola m68k, SPARC, MIPS

- ▶ Bi-Endian (wählbar): Alpha, ARM, (MIPS), (POWERPC)

- Arabische Zahlen, Netzwerk-Byteorder (Internet): Big Endian

- Mischformen möglich, aber nicht sonderlich verbreitet!

## **Endianess** I

#### Mehrere Bytes pro Zahl

- ▶ Betrachte Zahl 0x12345678 im Speicher an Position 0x1000

- ▶ Mehrere Bytes erforderlich ⇒ Unterschiedliche Anordnungen möglich

| Speicheradresse | 0 <i>x</i> 1000 | 0 <i>x</i> 1001 | 0 <i>x</i> 1002 | 0 <i>x</i> 1003 |

|-----------------|-----------------|-----------------|-----------------|-----------------|

| Big Endian      | 12              | 34              | 56              | 78              |

| Little Endian   | 78              | 56              | 34              | 12              |

#### Vorteile

- Big Endian: (Speicher) Dumps von Zahlen leichter zu lesen; Standard f

ür Daten

übertragung im Internet

- Little Endian: Triviale Casts zwischen verschiedenen Bitbreiten

イロト イポト イラト イラト 一日

Datenverarbeitungssysteme Datenrepräsentation und -manipulation Endianess

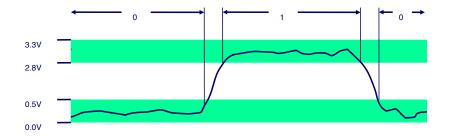

## **Endianess II**

Abbildungsquelle: Procedure Call Standard for the ARM Architecture

イロト イポト イヨト イヨト 二日一

Datenverarbeitungssysteme Datenrepräsentation und -manipulation Endianess

## **Endianess III**

#### Standardtest aus GNU Autoconf

```

// 0: big endian, 1: little endian

int endianess() {

uint32_t i=0x01234567;

return (*((uint8_t*)(&i))) == 0x67;

}

```

◆□▶ ◆□▶ ◆三▶ ◆三▶ ● □ ● ●

## **Endianess IV**

Endianess häufig transparent für Programmierer (bsp. beim *logischen* Links-Shift):

```

uint32_t value = 0x0000F000; // Little Endian: 00 F0 00 00

printf("Wert vor Shift : %#.8x\n", value); // Gibt immer

0x0000F000 aus

value = value << 1; // Logischer Links-Shift

printf("Wert nach Shift: %#.8x\n", value); // Gibt immer

0x0001E000 aus

// Speicherbelegung:

// - auf Little Endian (x86): 00 E0 01 00

// - auf Big Endian (MIPS): 00 01 E0 00</pre>

```

- Unterschiedliche Bit-Operation, gleiches Resultat

- Relevant für Systemprogrammierung: Kommunikation mit Geräten, Low-Level-Netzwerkprotokolle, Datenträgeraustausch zwischen Maschinen, ...

イロン 不得 とくほ とくほう 二日

## Daten untersuchen

```

void print_bytes(void *val, int len) {

uint8_t *ptr = (uint8_t*)val;

int count;

for (count = 0; count < len; count++) {

printf("0x%x: %.2x", &ptr[count], ptr[count]);

}

}</pre>

```

◆□▶ ◆□▶ ◆三▶ ◆三▶ ● □ ● ●

# Zeichendarstellung I

## Zeichendarstellung

- Buchstaben und Zeichenketten: Darstellung durch Bitstring, d.h. anderes Alphabet

- Code: Konvention zur Abbildung zwischen Alphabeten:

- ASCII-Code: Abbildung 7/8 Bits (fixe Anzahl!) auf Buchstaben

- ▶ Morse-Code: Abbildung variabler Anzahl ({-, -} auf Buchstaben

- Zeichenketten durch Aneinanderreihung von Bits erzeugen

- ► Achtung: Code ≠ Font (Zeichen vs. Glyphen)

イロト イポト イヨト イヨト 二日

## Zeichendarstellung II

|   | ASCII Code Chart |     |     |     |     |     |     |     |     |    |     |     |    |    |    |     |

|---|------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|-----|----|----|----|-----|

|   | 0                | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9  | Α   | В   | С  | D  | Е  | F   |

| 0 | NUL              | SOH | STX | ETX | EOT | ENQ | ACK | BEL | BS  | HT | LF  | VT  | FF | CR | S0 | SI  |

| ī | DLE              | DC1 | DC2 | DC3 | DC4 | NAK | SYN | ETB | CAN | EM | SUB | ESC | FS | GS | RS | US  |

| 2 |                  | !   |     | #   | \$  | °\0 | &   |     | (   | )  | *   | +   | ,  | -  | ·  | /   |

| 3 | 0                | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9  | :   | ;   | <  | =  | >  | ?   |

| 4 | 0                | Α   | В   | С   | D   | Е   | F   | G   | Η   | I  | J   | К   | L  | М  | Ν  | 0   |

| 5 | Р                | Q   | R   | S   | Т   | U   | ٧   | W   | Х   | Y  | Z   | [   | \  | ]  | ^  | _   |

| 6 | `                | а   | b   | с   | d   | е   | f   | g   | h   | i  | j   | k   | ì  | m  | n  | 0   |

| 7 | р                | q   | r   | s   | t   | u   | v   | W   | х   | У  | z   | {   |    | }  | ~  | DEL |

Bildquelle: Wikipedia

▲□▶▲□▶★□▶★□▶ = つくで

# Zeichendarstellung III

#### Unicode

- Weltweit verwendete Schriftsysteme/Zeichen: Deutlich mehr als 2<sup>8</sup> Zeichen

- Unicode: Soll *alle* früher und heute verwendeten Zeichen enthalten. Organisiert in 17 *Ebenen* mit je 2<sup>16</sup> Zeichen. Unterschiedliche Kodierungen:

- UTF-8 (Linux, Plan 9, Internet): 128 Zeichen deckungsgleich mit ASCII; zwei Bytes für (u.A.) deutsche Umlaute, 4 Bytes für allgemeine Zeichen

- UTF-16 (Windows, Java, Mac OS X): Zeichen dargestellt durch zwei oder vier Bytes

- UTF-32: 4 Bytes für jedes Zeichen

- Kodierung mit variabler Länge: Mehr Rechenaufwand; mit fester Länge: Mehr Speicherplatz

- UTF-16 und UTF-32: Endianess der Kodierung relevant!

イロト 不得 トイラト イラト 二日

## Zeichendarstellung IV

| Bereich              | Binärwerte                          |

|----------------------|-------------------------------------|

| 0x0 - 0x007F         | 0xxxxxxx                            |

| 0x0080 - 0x07FF      | 110xxxxx 10xxxxxx                   |

| 0x0800 - 0000FFFF    | 1110xxxx 10xxxxxx 10xxxxxx          |

| 0x10000 - 0x0010FFFF | 11110xxx 10xxxxxx 10xxxxxx 10xxxxxx |

(日)

## Gleitkommazahlen I

#### Zahlmengen

- N: Abzählbar unendlich, geschlossenes Intervall: endlich viele Werte

- Q: Abzählbar unendlich, geschlossenes Invervall: Unendlich viele Werte

- ▶ ℝ: Überabzählbar unendlich

- Rationale und reelle Zahlen nur approximativ darstellbar

#### Kodierung

- Zahlendarstellung basierend auf Bitstring

- Interpretation komplizierter als bei ganzen Zahlen

- Darstellbares Intervall wichtiger als genauere Approximation von Zahlen

イロト イポト イヨト イヨト 二日

## Gleitkommazahlen II

#### Darstellung rationaler/reeller Zahlen

Unterschiedliche äquivalente Schreibweisen:

$$c_0 = 299792458 \frac{m}{s}$$

= 299792, 458 \cdot 10<sup>3</sup>  $\frac{m}{s}$

= 0, 299792458 \cdot 10<sup>9</sup>  $\frac{m}{s}$

= 2, 99792458 \cdot 10<sup>8</sup>  $\frac{m}{s}$

- Normalisierung: Darstellung mir nur einer Ziffer vor Dezimaltrenner. Basis 2: Entweder o oder 1. Erster Fall trivial, daher immer 1.

- Zuätzliches (Gratis-)Bit an Präzision

イロト 不得 トイラト イラト 二日

## Gleitkommazahlen III

Allgemeine Repräsentation

Generelle Form:  $x = s \cdot m \cdot b^e$

- ► Vorzeichen *s*: ±1

- Mantisse m

- Basis b: Bei Menschen 10, bei Computern 2

- Exponent e

## Einflussfaktoren

- Mantisse: Genauigkeit

- Exponent: Zahlenumfang

イロト イポト イラト イラト 一日

## Gleitkommazahlen III

IEEE754: Definiert Standardformate mit  $\approx$ 7 bzw. 15 dezimalen Stellen relativer Genauigkeit:

| 31   | 30           | 29 | 28 | 27 | 26 | 25 | 24         | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13  | 12  | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|--------------|----|----|----|----|----|------------|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|----|---|---|---|---|---|---|---|---|---|---|

| S    | S Exponent E |    |    |    |    |    | Mantisse M |    |    |    |    |    |    |    |    |    |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |

| 63.6 | 63 62 52 51  |    |    |    |    |    |            |    |    |    |    |    |    |    |    |    |    |     |     |     |    |   |   |   |   |   |   |   |   |   | 0 |

| S    | S Exponent E |    |    |    |    |    |            |    |    |    |    |    |    |    |    | 1  | Мa | nti | iss | e N | Л  |   |   |   |   |   |   |   |   |   |   |

- Einfache Genauigkeit: |S| = 1, |E| = r = 8, |M| = p = 23

- Doppelte Genauigkeit: |S| = 1, |E| = 11, |M| = 52

Interpretation Bitmuster zu  $x = s \cdot m \cdot b^e$

▶  $s = (-1)^S$

- m = 1, M (Kommazahl!) respective  $m = 1 + \frac{M}{2^p}$

- e = E B (*Biaswert*  $B = 2^{r-1} 1$  zur Darstellung negativer Exponenten)

- Beispiel: Siehe Tafel

## Gleitkommazahlen III

IEEE754: Definiert Standardformate mit  $\approx$ 7 bzw. 15 dezimalen Stellen relativer Genauigkeit:

| 31    | 30           | 29 | 28  | 27  | 26  | 25   | 24 | 23 | 22         | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|----|-----|-----|-----|------|----|----|------------|----|----|----|----|----|----|----|----|----|-----|-----|----|---|---|---|---|---|---|---|---|---|---|

| S     |              | I  | Exp | 001 | ner | nt ] | E  |    |            |    |    |    |    |    |    |    |    | М  | lan | tis | se | Μ |   |   |   |   |   |   |   |   |   |

| 63.63 | 6362 52 51   |    |     |     |     |      |    |    |            |    |    |    |    |    |    |    |    |    |     |     |    |   |   |   |   |   |   |   |   |   | 0 |

| S     | s Exponent E |    |     |     |     |      |    |    | Mantisse M |    |    |    |    |    |    |    |    |    |     |     |    |   |   |   |   |   |   |   |   |   |   |

- Einfache Genauigkeit: |S| = 1, |E| = r = 8, |M| = p = 23

- Doppelte Genauigkeit: |S| = 1, |E| = 11, |M| = 52

## Extremale Zahlen: Einfache Genauigkeit

- ► Kleinste normalisierte Zahl:  $\pm 1, 0 \cdots 0 \times 2^{-126} \approx \pm 1, 18 \cdot 10^{-38}$

- Größte Zahl:  $\pm 1, 1 \cdots 1 \times 2^{127} \approx \pm 3, 4 \cdot 10^{38}$

イロト イポト イモト イモト 二日

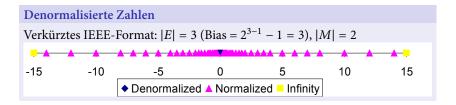

## Gleitkommazahlen IV

#### Sonderfälle

- NaN (*not a number*), beispielsweise  $\frac{1}{0}$

- ▶ Singularitäten (±∞)

- Denormalisierte Zahlen: Nahe an o

#### Denormalisierte Zahlen

- Exponent kodiert als 0x0

- Interpretation: 1 B (*nicht* 0 B!)

- Mantisse: Implizite führende o (*nicht* 1)

- Präzisionsverlust für  $\lim_{x\to 0} x$

- Zwei Nullwerte: ±0 (Limes!)

## Gleitkommazahlen IV

#### Sonderfälle

- NaN (*not a number*), beispielsweise  $\frac{1}{0}$

- ▶ Singularitäten (±∞)

- Denormalisierte Zahlen: Nahe an o

Abbildung basiert auf Bryant & O'Hallaron

イロト イポト イヨト イヨト 二日

## Gleitkommazahlen IV

#### Sonderfälle

- NaN (*not a number*), beispielsweise  $\frac{1}{0}$

- ▶ Singularitäten (±∞)

- Denormalisierte Zahlen: Nahe an o

# Denormalisierte ZahlenVerkürztes IEEE-Format: |E| = 3 (Bias = $2^{3-1} - 1 = 3$ ), |M| = 2-1-0.500.51 $\bullet$ Denormalized Normalized Infinity

Abbildung basiert auf Bryant & O'Hallaron

イロン 不得 とくほ とくほう 二日

## Gleitkommazahlen V

#### NaN und $\pm \infty$

- Exponent in beiden Fällen 111...1

- ► Mantisse 000...0: ±∞

- Not a Number (NaN): Mantisse ≠ 000...0

#### Zusammenfassung (Single Precision)

| Exponent | Mantisse | Objekt               |

|----------|----------|----------------------|

| 0        | 0        | Null                 |

| 0        | ≠ 0      | Denormalisierte Zahl |

| 1254     | beliebig | Normalisierte Zahl   |

| 255      | 0        | ±∞                   |

| 255      | ≠ 0      | NaN                  |

## Gleitkommazahlen VI

#### Rechen

- Prinzip:  $a \odot_{\text{fp}} b = \text{round}(a \odot b)$

- Unabhängig von konkreter Implementierung

## Eigenschaften

- Kommutativgesetz gilt:  $a \odot b = b \odot a$

- Keine Assoziativität:  $a \odot (b \odot c) \neq (a \odot b) \odot c$

- Beispiel:

(3.141 + 10<sup>20</sup>) 10<sup>20</sup> = 0,

3.141 + (10<sup>20</sup> 10<sup>20</sup>) = 3.141

- Keine Distributivität:  $a \cdot (b + c) \neq a \cdot b + a \cdot c$

- Compileroptimierungen problematisch

(日)

## Gleitkommazahlen VII

**Beispiel: Multiplikation**

$$(-1)^{S_1} \cdot M_1 \cdot 2^{E_1} \times (-1)^{S_2} \cdot M_2 \cdot 2^{E_2} = (-1)^S \cdot M \cdot 2^E$$

•

$$S = S_1 \oplus S_2$$

,  $M = M_1 \cdot M_2$ ,  $E = E_1 + E_2$

- Wenn  $M \ge 2$  **so Rechtsshift und** *E* erhöhen

- ▶ Wenn *E* zu groß ☞ Overflow

- ► *M* auf passende Bitanzahl runden

(日)

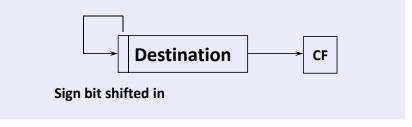

# Bitoperationen

## Boole'sche Algebra

- Formale Grundlage vieler Bitoperationen

- Algebraische Darstellung der Logik

- ▶ »Wahr« = 1

- ► »Falsch« = o

- Auch f

ür Bitvektoren definiert!

#### Wahrheitstabellen & 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 1 1 Λ 0 0 ~ 0 1 0 0 1 1 0 1 1 0

(日)

э

## **Bitoperationen II**

Anwendung auf Bitvektoren: Siehe Tafel

(日)

## **Bitoperationen III: Mengen**

#### Darstellung von Mengen

- ▶ Nützlich bei Statusflags (µController, Betriebssysteme, ...)

- Elemente der Menge durch Bits kodiert

## Kodierung

- Bitvektor mit w Bits: Teilmenge  $\{0, \dots, w-1\}$

- ▶ Interpretation als Flags: {*A*, *B*, *C*, *D*, *E*, *F*, ... }

- $w_j = 1$  wenn  $j \in w$

- Beispiel:

- 01101001 = {G, F, D, A} (HGFEDBCA)

- ▶ 01010101 = {G, E, C, A} (HGFEDCBA)

・ロト ・ 理 ト ・ ヨ ト ・

## **Bitoperationen III: Mengen**

#### Darstellung von Mengen

- Bitvektoren repräsentieren Mengen

- ▶ Nützlich bei Statusflags (µController, Betriebssysteme, ...)

- Elemente der Menge durch Bits kodiert

#### Operationen

- ► &: Schnittmenge ☞ 01000001 = {A, G}

- ▶ |: Vereinigungsmenge ☞ 0111101 = {A, C, D, E, F, G}

- ▶ ^: Symmetrische Differenz ☞ 0011100 = {C, D, E, F}

- ▶ ~: Komplement ☞ 10101010 = {B, D, F, H}

イロト 不得 トイラト イラト 二日

## **Bitoperationen IV**

Trick: Komplement und Inkrement

- ▶ ~x + 1 == -x

- ▶ Gilt, da ~x + x == -1

- Veranschaulichung: Siehe Tafel

#### Trick: Inverses eines Wertes

- Komplementbildung:  $a \otimes \neg a = 0 \forall a$

- »Ausnullen« von Registern

## **Trick: Flags testen**

- Idempotenz:  $a|a = a \forall a$

- ▶ Testen auf *exakten* Satz an Flags: (var | FLAGS) == FLAGS

## **Bitoperationen** V

## Bitoperationen in C

- Operatoren: &, |, ~, ^

- Definiert auf allen integralen Datentypen (short, int, long, unsigned, char)

- Bitweise Bearbeitung der Argumente

## Logische Operationen

- Operatoren: ۵۵, ۱۱, !

- Unterschiedliche Wahrheitstabelle

- o = »Falsch«

- Alles andere: »Wahr«

- Bit als Rückgabewert

- Partielle Auswertung!

## Inhalt

#### Überblick und Einführung Literatur Lernziele

#### Datenrepräsentation und -manipulation

Zahlendarstellung Endianess Zeichendarstellung Gleitkommazahlen Bitoperationen

#### Prozessorarchitektur

Grundkoperationen einer CPU von Neumann- und Harvard-Architektur Grundkonzept der Befehlsausführung Befehlszyklen und Pipelines Optimierungsmechanismen Sonstige Themen Hochsprachen und Assembler I

Instruktionsets Die Werkzeugkette ARM-Assembler ARM-Assembler ARM-Assemblerprogrammierung Befehlsgruppen Speicheraufbau Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken Hochsprachen & Compiler Aufgaben und Überblick Syntaxanalyse Semantische Analyse & Codegenerierung Optimierungen

#### Speicherhierarchie, Caches und MMUs

RAM-Speicher Festplatten und Massenspeichergeräte CPU-Speicher-Kluft und Lokalität Caches Caches-Optimierungen Virtueller Speicher und Memory Management Units

#### Betriebssysteme

Grundstruktur Memory Management Unit und Adressrauwnerwaltung Interrupts Ausprägungen von BS Fallbeispiel: Linux Blockgeräte und Dateisysteme

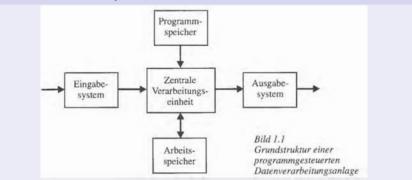

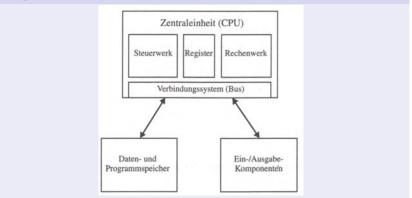

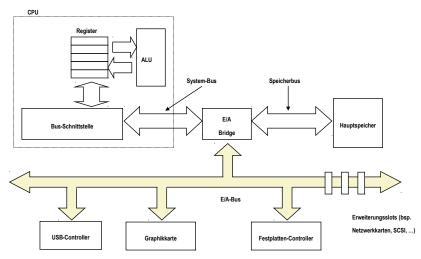

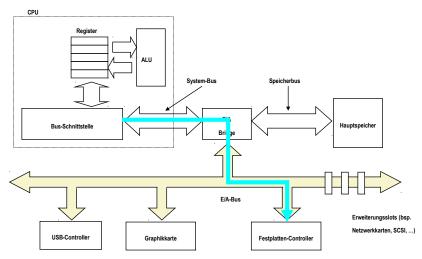

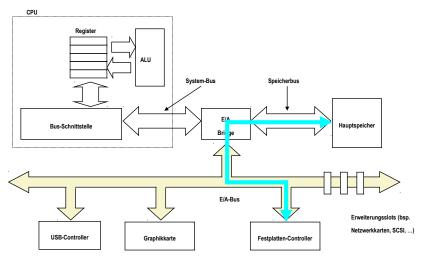

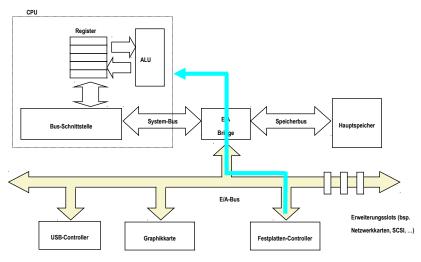

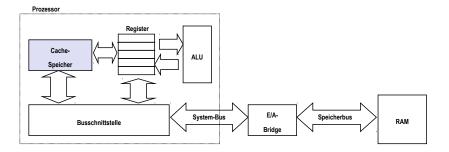

## Datenverarbeitungssystem

#### Grundstruktur DV-System

Kernelement: Zentrale Verarbeitungseinheit (*Central Processing Unit, CPU*) – (Mikro)Prozessor

Abbildung: Taschenbuch der Mikroprozessortechnik, Fachbuchverlag Leipzig

イロト イポト イラト イラト 一日

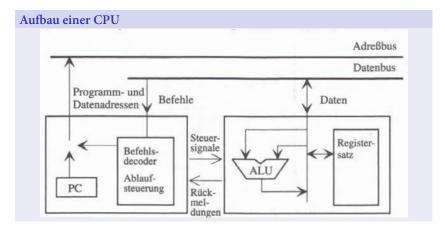

## Prozessorarchitektur I

#### Komponenten eines Prozessors

Abbildung: Taschenbuch der Mikroprozessortechnik, Fachbuchverlag Leipzig

## Prozessorarchitektur II

#### Halbleiterschaltungen

- ASIC (Application Specific Integrated Circuit): In Silizium

»gegossene« elektronische Spezialschaltung

- FPGA (*Field Programmable* Gate Array): Rekonfigurierbare Schaltung

- IC: Vielzweckprozessor

#### Prozessortypen

- Vielzweckprozessoren

- Hochleistungsprozessoren

- Vektorprozessoren

- Signalprozessoren (Digital Signal Processors – DSP)

イロト 不得 トイラト イラト 二日

## Prozessorarchitektur III

#### Eigenschaften von Vielzweckprozessoren

- Keine Spezialisierung

- Einsatzweck a priori unbekannt

- Universelle, dynamische Programmierbarkeit

- Einfache Elementarbefehle

- Schnelle Ausführung von Elementarbefehlen

イロト イポト イヨト イヨト 二日

## Prozessorarchitektur IV

Abbildung: Taschenbuch der Mikroprozessortechnik, Fachbuchverlag Leipzig

# Grundoperationen einer CPU I

- Arithmetische Funktionen

- Ganzzahl- und Gleitkommaarithmetik, Formatkonvertierung, Sign Extension, ...

- Logische Funktionen und Bitoperationen

- Vergleiche, And, Or, Bit-Shifting, Negation, ...

- Speicherzugriff

- Lesen und Schreiben von Speicherwerten

- Bedingungen und Sprünge

- Unterbrechungen

- Speicherverwaltung und Betriebssystemunterstützung

- Spezialbefehle

- Verschlüsselung, Hashing, FFT, Performancemessung, Debugging, Diagnose ...

イロト イポト イヨト イヨト 二日

- Prozessorarchitektur

- Grundoperationen einer CPU

# Grundoperationen einer CPU II

#### Gegeben

- Programm im Speicher

- Grundfunktionen in Instruktionen kodiert

- Interpretation binärer Daten

- Herstellerabhängige Kodierung

- Daten im Speicher

#### Arbeitsweise: Phasen

- 1. Neue Instruktion aus Speicher ins Steuerwerk laden (*fetch*)

- 2. Instruktion auswerten (*decode*)

- 3. Benötigte Daten aus Speicher ins Rechenwerk lesen, Daten gemäß Instruktion verarbeiten und Ergebnis in Speicher schreiben (*execute*)

(日)

4. Weiter bei 1

Aktuelle Position im Programm: Befehlszähler (Program Counter)

Prozessorarchitektur

von Neumann- und Harvard-Architektur

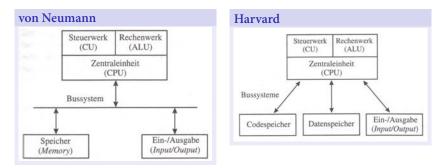

## von Neumann/Harvard-Architektur

## Moderne Rechner

- Mischform aus beiden Konzepten

- Daten und Code gemeinsam im RAM, aber Aufteilung bei Caches

Abbildung: Taschenbuch der Mikroprozessørtechnik, Fachbuchverlag Leipzig 🦿 🔍 🔍

Prozessorarchitektur

von Neumann- und Harvard-Architektur

## Intermezzo: Zeiger

## Zeiger (Pointer)

- Direkter Zugriff auf den Speicher

- Systemsoftware, Simulatoren, High Performance

- Ähnliche Sicht wie aus Assembler-Ebene

- Leistungsfähig, aber gefährlich

#### **Bjarne Stroustrup**

C makes it easy to shoot yourself in the foot.

イロト イポト イラト イラト 一日

Prozessorarchitektur

von Neumann- und Harvard-Architektur

## Intermezzo: Zeiger

## Zeiger (Pointer)

- Direkter Zugriff auf den Speicher

- Systemsoftware, Simulatoren, High Performance

- Ähnliche Sicht wie aus Assembler-Ebene

- Leistungsfähig, aber gefährlich

#### **Bjarne Stroustrup**

C makes it easy to shoot yourself in the foot; C++ makes it harder.

## Intermezzo: Zeiger

#### Zeiger (Pointer)

- Direkter Zugriff auf den Speicher

- Systemsoftware, Simulatoren, High Performance

- Ähnliche Sicht wie aus Assembler-Ebene

- Leistungsfähig, aber gefährlich

#### Bjarne Stroustrup

C makes it easy to shoot yourself in the foot; C++ makes it harder, but when you do it blows your whole leg off.

イロト イポト イヨト イヨト 二日

## Intermezzo: Zeiger

#### Zeiger-Beispiel o

```

int i[2] = \{ 42, 23 \};

1

2

int x = 4711:

3

int *xptr = &x;

4

5

int *iptr = &i[0];

6

7

printf("x vor Zeiger-Operation: %d\n", x);

8

*xptr = 1147;

9

printf("x nach Zeiger-Operation: %d\n\n", x);

10

printf("&i[0]: %p, &i[1]: %p\n", &i[0], &i[1]);

11

printf("Differenz &i[1] - &i[0]: %lu\n", &i[1]-&i[0]);

12

printf("Void-Differenz &i[1] - &i[0]: %lu\n\n",

13

(void*)&i[1]-(void*)&i[0]);

14

printf("iptr: %p, iptr+1: %p\n", iptr, iptr+1);

15

```

イロト イポト イヨト イヨト 二日

von Neumann- und Harvard-Architektur

## Intermezzo: Zeiger

#### Zeiger-Beispiel 1

```

unsigned long 1 = ULONG MAX;

1

unsigned int i[2] = { 0, 1 };

2

unsigned int *iptr = &i[0];

3

4

unsigned long *iptr2 = (unsigned long*)&i[0];

5

6

printf("i[0]: %u, i[1]: %u\n", i[0], i[1]);

7

8

*iptr = 1;

printf("i[0]: %u, i[1]: %u\n", i[0], i[1]);

9

10

*iptr2 = 1;

11

printf("i[0]: %u, i[1]: %u\n", i[0], i[1]);

12

```

イロト イポト イヨト イヨト ニヨー

## Intermezzo: Zeiger

Zeiger-Beispiel 2

```

struct collection {

1

2

int a, b, c;

unsigned long d;

3

};

4

5

6

struct collection c[2];

7

struct collection *cptr = &c[0];

8

printf("sizeof(int): %lu, sizeof(long): %lu\n", sizeof(int),

9

sizeof(long));

printf("sizeof(collection): %lu\n\n", sizeof(struct

10

collection));

11

printf("&c[0]: %p, &c[1]: %p\n\n", &c[0], &c[1]);

12

printf("Differenz &c[1] - &c[0]: lun", &c[1]-&c[0]);

13

printf("Differenz (void*)&c[1] - (void*)&c[0]: %lu\n",

14

(void*) &c[1] - (void*) &c[0]);

15

16

printf("cptr: %p, cptr+1: %p\n", cptr, cptr+1);

```

## Intermezzo: Zeiger

#### Zeiger-Beispiel 3

```

#define offsetof(type, element) \

1

((size t) & (((type *) 0) -> element))

2

3

struct collection {

4

5

int a:

6

int b;

int c:

7

8

unsigned long d;

9

};

10

printf("offset(a): %lu\n", offsetof(struct collection, a));

11

printf("offset(b): %lu\n", offsetof(struct collection, b));

12

printf("offset(c): %lu\n", offsetof(struct collection, c));

13

printf("offset(d): %lu\n", offsetof(struct collection, d));

14

```

イロト 不得 トイヨト イヨト ニヨー

Grundkonzept der Befehlsausführung

# Befehlsausführung I

Befehlsphasen

Fetch  $\rightarrow$  Decode  $\rightarrow$  Execute

### Register

- Rechnungsoperanden, Speicheradressen etc. in schnellen, winzigen Speichern (Register) im Prozessor vorgehalten

- ► Typischerweise 32 oder 64 Bits *Wortbreite* (µController: 8 und 16 Bits)

イロト イポト イヨト イヨト 二日

Grundkonzept der Befehlsausführung

# Befehlsausführung II: iSMPL

### Beispielarchitektur iSMPL

## Mischung aus ARM und x86:

- 8 Register: (R<sub>o</sub>), ..., (R<sub>5</sub>), SP (Stack Pointer), PC (Program Counter)

- 32 Bit Wortbreite

- Befehlslänge: 8–44 Bits

- 4 Bits zur Kodierung Opcode

- Statusregister: Zero, Less, Greater

## Instruktionen (Mnemonics)

- nop: No Operation

- Speicherzugriff: load, store (Speicher/Register)

- Arithmetik: add, sub, cmp (Compare)

- Bitoperationen: and, or, xor

- Sprünge: jmp (unkonditional), jlt, jgt (less/greater than), jeq (equal), jne (not equal)

イロト イポト イラト イラト 一日

- Grundkonzept der Befehlsausführung

# Befehlsausführung III

### Fetch: Instruktion laden

- Speicherinhalt an Position des Befehlszählers lesen (Dereferenzieren!)

- Befehlszähler erhöhen

### Decode: Instruktion auswerten

- ▶ Instruktion: Operationscode (Opcode) und Argumente

- Argumente: Speicheradressen oder Registernamen

- ▶ ☞ Komponenten auswerten und an Rechenwerk übergeben

イロト イポト イヨト イヨト 二日

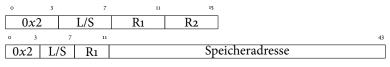

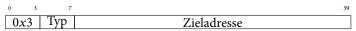

# Befehlsausführung IV: iSMPL-Kodierung

Nop:

| o | 3   |     | 7 |

|---|-----|-----|---|

| ( | 0x0 | 0x0 |   |

Arithmetik + Logik:

| 0  | 3    | 7   | 11 | 15 | 19 |

|----|------|-----|----|----|----|

| 0x | :1 ' | Гур | R1 | R2 | R3 |

► Speicher:

Sprünge:

イロト イポト イヨト イヨト

Grundkonzept der Befehlsausführung

# Befehlsausführung V

## Execute: Befehlsausführung

Typischerweise aufgespalten in mehrere Aktionen (Anzahl Hersteller- und CPU-abhängig):

- Operanden aus Speicher holen (*operand fetch*)

- Operation ausführen (*execute*), Wirkung je nach Opcode)

- Ergebnis schreiben (writeback), Speicher/Register

イロト イポト イラト イラト 一日

Grundkonzept der Befehlsausführung

## Befehlsausführung VI: Beispiele iSMPL

#### Addition zweier Zahlen

load r1, 0x0 load r2, 0x4 add r1, r1, r2 store r1, 0x8

- Speicher byteweise adressiert # 32-Bit-Werte im Abstand 0x4

- Register (R<sub>1</sub>)

»wiederverwendet«

### Zeiger dereferenzieren

load r1, 0x0

load r2, r1

- Speicherinhalt an Position 0x0 : 0x100

- Inhalt Register (R<sub>2</sub>): Inhalt von Speicherzellen

(0x100, 0x101, 0x102, 0x103)

イロト イポト イヨト イヨト 二日

# Befehlsausführung VII

## Bedingungen und Sprünge

- Bislang: Lineare Ausführung, keine Sprünge

- Probleme:

- Nach welche Kriterien springen?

- Keine »Kommunikation« zwischen den Befehlen

- Lösung: Statusregister mit Flags, bsp.

- Overflow

- Less (equal), Greater (equal)

- Carry

- Zero

## Ablaufdiagramm: Siehe Tafel

#### **Beispiel**

```

load r1, 0x0

load r2, 0x4

cmp r1, r2

jne L1 // r1 != r2?

<Anweisungen fuer Ergebnis r1 == r2>

...

jmp L2

L1:

<Anweisungen fuer Ergebnis r1 != r2>

...

L2:

<Gemeinsamer Pfad>

```

## Sprungimplementierung

Sprung = Veränderung Befehlszähler

くロ とうぼう く ヨ とう

Grundkonzept der Befehlsausführung

## Befehlsausführung VIII

## Schleife

```

load r1, 0x0

load r2, 0x4

load r3, 0x8

L1:

// Schleifenkoerper: Aktion durchfuehren

sub r1, r1, r3

cmp r1, r2 // Schleifenzähler == 0?

jne L1 // Nein, Schleife nochmals durchlaufen

L2:

// Code nach Schleife

```

### Speicherinhalt:

- ► 0*x*0: 10

- ▶ 0*x*4: o

- ► 0*x*8:1

イロト イポト イヨト イヨト ニヨー

# **RISC versus CISC**

## CISC (bsp. x86)

- Complete Instruction Set Computer

- Viele, teilweise hochkomplexe Instruktionen (pclmullqlqdq...)

- Potentiell lange Instruktionsdauer (z.B. Speicherblöcke kopieren)

- Variable Instruktionslänge

- Operationen direkt im Speicher möglich

- Funktionsparameter: Stack

## RISC (bsp. MIPS, ARM)

- Reduced Instruction Set Computer

- Wenige, sehr elementare Instruktionen

- Schnelle Instruktionsausführung

- Feste Instruktionslänge

- Load/Store-Prinzip

- Funktionsparameter: Register

イロト イポト イヨト イヨト 二日

Befehlszyklen und Pipelines

# Befehlszyklen I

## Gesamtablauf

- Assembler-Befehl: Mehrere Phasen

- Synchronisation notwendig:

- ▶ Fetch beendet  $\rightarrow$  Decode beginnen,

- ▶ Decode beendet  $\rightarrow$  Execute beginnen, ...

- Gemeinsamer Takt in allen CPU-Komponenten verfügbar

## Taktfrequenz

► Taktung: CPU-Frequenz, z.B. 700 MHz oder 2.2 GHz:

$$f = 700 \text{ MHz} = 700 \cdot 10^6 \frac{1}{s} = 7 \cdot 10^8 \frac{1}{s} = \frac{1}{\Delta t}$$

$$\Delta t = \frac{1}{f} = 1/7 \cdot 10^{-8} \approx 1.43 \text{ ns}$$

▶ Höhere Frequenz  $\rightarrow$  Schnellere Verarbeitung

Befehlszyklen und Pipelines

# Befehlszyklen I

## Gesamtablauf

- Assembler-Befehl: Mehrere Phasen

- Synchronisation notwendig:

- ▶ Fetch beendet  $\rightarrow$  Decode beginnen,

- ▶ Decode beendet  $\rightarrow$  Execute beginnen, ...

- Gemeinsamer Takt in allen CPU-Komponenten verfügbar

## Taktfrequenz

► Taktung: CPU-Frequenz, z.B. 700 MHz oder 2.2 GHz:

$$f = 700 \text{ MHz} = 700 \cdot 10^6 \frac{1}{\text{s}} = 7 \cdot 10^8 \frac{1}{\text{s}} = \frac{1}{\Delta t}$$

$$\Delta t = \frac{1}{f} = 1/7 \cdot 10^{-8} \approx 1.43 \text{ ns}$$

► *Aber*: Höhere Frequenz → Höherer Stromverbrauch

Befehlszyklen und Pipelines

# Befehlszyklen II

## Zyklentypen

- Befehlszyklus: Abarbeitung einer Assembler-Instruktion

- Maschinenzyklus: Abarbeitung einer Befehlsphase (Fetch etc.)

- ► Taktzyklus: Elementare Zeiteinheit der CPU

## Herausforderungen

- Anzahl Takte pro Zyklus variiert

- Prinzipbedingt: Unterschiedlich lang kodierte Instruktionen

- Variabel: Dauer Speicherzugriff (Caches, NUMA-Systeme, ...)

- Nicht alle Maschinenzyklen f

ür alle Befehlstypen notwendig (Beispiel: Kein Writeback bei Sprung)

- Komplexe Ablaufsteuerung (endlicher Automat!)

## Illustration: Siehe Tafel

(日)

Befehlszyklen und Pipelines

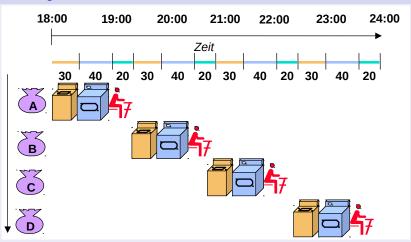

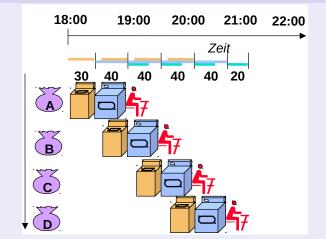

# **Pipelining I: Waschtag**

Waschtag in der WG

Befehlszyklen und Pipelines

# Pipelining I: Waschtag

## Waschtag in der WG

Befehlszyklen und Pipelines

# **Pipelining II**

## Pipelining auf CPUs

IF ID OF IE WB IF ID OF IE WB

## Grenzen des Pipelinings

- Komplexität (gleich lange Stages konstruieren)

- Nicht verwendete Stages

- Stalls durch Konflikte

・ロト ・ 聞 ト ・ 臣 ト ・ 臣 ト

Befehlszyklen und Pipelines

# **Pipelining II**

| Pipelining auf CPUs |    |    |    |    |    |    |    |    |    |    |

|---------------------|----|----|----|----|----|----|----|----|----|----|

| 1                   | IF | ID | OF | IE | WB |    |    |    |    |    |

| 2                   |    | IF | ID | OF | IE | WB |    |    |    |    |

| 3                   |    |    | IF | ID | OF | IE | WB |    |    |    |

| 4                   |    |    |    | IF | ID | OF | IE | WB |    |    |

| 5                   |    |    |    |    | IF | ID | OF | IE | WB |    |

| 6                   |    |    |    |    |    | IF | ID | OF | IE | WB |

#### Grenzen des Pipelinings

- Komplexität (gleich lange Stages konstruieren)

- Nicht verwendete Stages

- Stalls durch Konflikte

イロト 不聞 とくき とくきとう き

Befehlszyklen und Pipelines

# **Pipelining II**

| Pipelining auf CPUs |    |    |    |    |    |    |    |    |    |    |

|---------------------|----|----|----|----|----|----|----|----|----|----|

| 1                   | IF | ID | OF | IE | WB |    |    |    |    |    |

| 2                   |    | IF | ID | OF | IE | WB |    |    |    |    |

| 3                   |    |    | IF | ID | OF | IE | WB |    |    |    |

| 4                   |    |    |    | IF | ID | OF | IE | WB |    |    |

| 5                   |    |    |    |    | IF | ID | OF | IE | WB |    |

| 6                   |    |    |    |    |    | IF | ID | OF | IE | WB |

## Grenzen des Pipelinings

- Komplexität (gleich lange Stages konstruieren)

- Nicht verwendete Stages

- Stalls durch Konflikte

イロト 不聞 とくき とくきとう き

Befehlszyklen und Pipelines

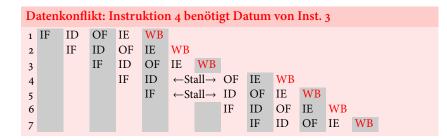

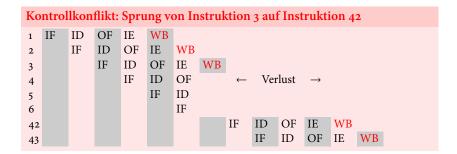

# Pipelining III: Konflikte

### Konflikte

- Datenkonflikt: Instruktion n + j benötigt Ergebnis von Instruktion n (Beispiel: Rechenoperand)

- Ressourcenkonflikt: Aufeinanderfolgende Instruktionen benötigen gleiche HW-Ressource

- *Kontrollkonflikt*: Adresse von Instruktion n + j hängt ab von Instruktion n (Beispiel: Sprung)

イロト イポト イラト イラト 一日

Befehlszyklen und Pipelines

# Pipelining IV: Konflikte II

イロト イポト イヨト イヨト

Befehlszyklen und Pipelines

# Pipelining V: Konflikte III

イロト イポト イヨト イヨト

# **Optimierungsmechanismen I**

## Superskalarität

- Statisches Scheduling: Befehlsfolge statisch; Anzahl paralleler Befehle dynamisch von CPU bestimmt

- Dynamisches Scheduling: CPU bestimmt Reihenfolge paralleler Befehle durch Umordnung (*out-of-order*)

- Very Long Instruction Word (VLIW): Mehrere Befehle pro Instruktion

| Il | Illustration: Zwei parallele Pipelines |    |    |    |    |     |     |  |  |  |  |   |     |   |     |     |   |    |  |

|----|----------------------------------------|----|----|----|----|-----|-----|--|--|--|--|---|-----|---|-----|-----|---|----|--|

|    |                                        |    |    |    |    | . 1 |     |  |  |  |  |   |     |   |     |     |   |    |  |

| 1  | IF                                     | ID | OF | IE | WB |     |     |  |  |  |  |   |     |   |     |     |   |    |  |

| 2  | IF                                     | ID | OF | IE | WB |     |     |  |  |  |  |   |     |   |     |     |   |    |  |

| 3  |                                        | IF | ID | OF | IE | WB  |     |  |  |  |  |   |     |   |     |     |   |    |  |

| 4  |                                        | IF | ID | OF | IE | WB  |     |  |  |  |  |   |     |   |     |     |   |    |  |

| 5  |                                        |    | IF | ID | OF | IE  | WB  |  |  |  |  |   |     |   |     |     |   |    |  |

| 6  |                                        |    | IF | ID | OF | IE  | WB  |  |  |  |  |   |     |   |     |     |   |    |  |

| 6  |                                        |    | IF | ID | OF | IE  | W B |  |  |  |  | • | < 7 | • | < ∃ | ÷ • | 4 | э. |  |

Optimierungsmechanismen

# **Optimierungsmechanismen II**

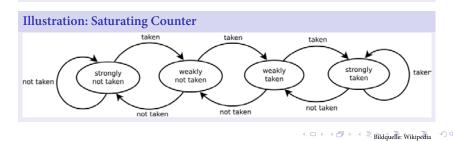

## Sprungvorhersage

- Vermeiden von Pipeline-Stalls bei Verzweigungen

- Sprungvorhersage (Branch Prediction):

- Statische Vorhersage (Beispiel: Rückwärts ja, vorwärts nein)

- Saturating Counter (Zustandsmaschine mit zwei Bits)

- Maschinelles Lernen zur Vorhersage aus Analyse der (globalen/lokalen)Historie

# Optimierungsmechanismen III

## Multi- und Many-Core

- Mehrere CPUs pro System

- Übliche Konfiguration (bis auf kleinste Systeme)

- CPUs: 2-16 Cores üblich; GPUs (Grafikkarten): Tausende

- Probleme: Synchronisierung, Arbeitsverteilung

## Multithreading

- Physikalischer Prozessorkern als mehrere virtuelle Kerne sichtbar

- Bessere Ausnutzung der statischen Ressourcen

## Arbeitsaufteilung

- Speedups nicht automatisch erzielbar

- Muss in Algorithmen, Systemsoftware etc. berücksichtigt werden!

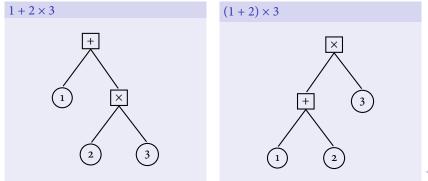

# Hochsprachen und CPUs

## Compiler

- ▶ *Compiler*: Konverter Hochsprachenprogramm  $\rightarrow$  Maschinenformat

- Spezifische Übersetzung je Maschinentyp (und Betriebssystem) erforderlich

| C-Beispiel                                 | Assembler-Code                                                                |

|--------------------------------------------|-------------------------------------------------------------------------------|

| <pre>int x, y, z;<br/><br/>x = y + z</pre> | load r1, &y<br>load r2, &z<br>add r0, r1, r2 // r0 <- r1 + r2<br>store r0, &x |

イロト イポト イヨト イヨト 二日

## Inhalt

#### Überblick und Einführung Literatur Lernziele

#### Datenrepräsentation und -manipulation

Zahlendarstellung Endianess Zeichendarstellung Gleitkommazahlen Bitoperationen

#### Prozessorarchitektur

Grundkoperationen einer CPU von Neumann- und Harvard-Architektur Grundkonzept der Befehlsausführung Befehlszyklen und Pipelines Optimierungsmechanismen Sonstige Themen

#### Hochsprachen und Assembler I

Instruktionssets Die Werkzeugkette ARM-Assembler ARM-CPU-Architektur ARM-Assemblerprogrammierung Befehsgruppen Speicheraufbau Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken & Compiler Aufgaben und Überblick Syntaxanalyse Semantische Analyse & Codegenerierung Optimierungen

#### Speicherhierarchie, Caches und MMUs

RAM-Speicher Festplatten und Massenspeichergeräte CPU-Speicher-Kluft und Lokalität Caches Caches-Optimierungen Virtueller Speicher und Memory Management Units

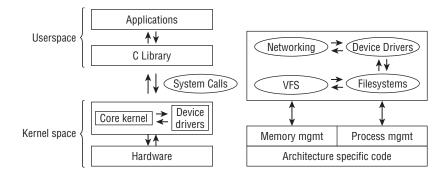

#### Betriebssysteme

Grundstruktur Memory Management Unit und Adressrauwnerwaltung Interrupts Ausprägungen von BS Fallbeispiel: Linux Blockgeräte und Dateisysteme

# Hochsprachen und Assembler

## System und ISA

- System: Hardware und Software

- »Grenzschicht«: Assembler.

- Instruction Set Architecture (ISA): Register, grundlegende Befehle, Speicherzugriff, Unterbrechungen, ...

- Kompatibilität wichtig: ISAs typischerweise abwärtskompatibel (Bsp. ARMv1, ⊆ ...⊆ ARMv8, IA32 ⊆ AMD64/EMT64)

### Systemdetails

- Coprozessoren, GPUs, Floating Point-Mechanismen

- Zubehörgeräte (Grafik, Sound, Netwerk, ...)

- Prozessor-Caches, Betriebsfrequenz(en)

- Mikroarchitektur: Implementierung einer ISA

## ISA ≠ Implementierung

Bsp. ARM: Intel, Qualcom, Freescale,

# **ARM: Allgemeines und Historie I**

### **ARM-Historie**

- ▶ 80er Jahre: Acorn Computers (Co-Prozessor für BBC Micro)

- Acorn RISC machine (ARM): Berkeley RISC-inspirierte CPU (Erster Simulator in Basic!)

- Archimedes: Erster ARM-Basierter Computer

- Transition zu Standard-Embedded-Prozessor (geringe Leistungsaufnahme, System-on-Chip (SoC))

- ARM Holdings: Kein HW-Produzent; Know-How-Verkauf

イロト イポト イヨト イヨト 二日

# **ARM: Allgemeines und Historie II**

## **ARM: Allgemeines**

- ▶ ISA: ARMv $x, x \in [1, 8]$

- Zahlreiche Hardware-Implementierungen (synthetisierte Cores!)

- Parameter wählbar: Core-Anzahl, Cache-Größen, etc.

- In »HW-Programmiersprache« beschrieben

- Momentan aktuell: ARMv4, ARMv4T, ARMv5T, ARMv5TE, ARMv5TEJ, ARMv6

- T: Thumb

- J: Java

- E: DSP-Instruktionen

- ARMv7: *Cortex*-Reihe mit Profilen Cortex- $y, y \in \{A, R, M\}$

- A: Anwendung (Application)

- R: HaRte Echtzeit (*Real-Time*)

- M: μController (*Microcontroller*)

(日)

# Kompatibilität von ISAs

## ISA-Kompatibilität

- Abwärtskompatibilität (*Jahrzehnte*!); neue Architekturen selten (Itanium...)

- ► Bsp.: ARMv4  $\subseteq$  ARMv5  $\subseteq$  ARMv6  $\subseteq$  ARMv7  $\subseteq$  ARMv8  $\subseteq$  ···

- Trend: Optionale Erweiterungen

### Vorteile

- Programme »für immer« (Branchenspezifische Software!)

- Prozessoren (relativ) direkt austauschbar

- ABI-Stabilität (Application Binary Interface) möglich

## Nachteile

Neue Programmierstile (Assembler → Hochsprachen): ISA-Möglichkeiten obsolet

(日)

HW-Leistung nicht optimal verwendet (bsp. Multicore)

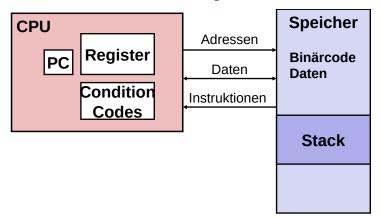

## System aus Sicht Assembler-Programmier/in

Abbildung basiert auf Bryant & O'Hallaron

イロト イポト イラト イラト 一日

## System aus Sicht Assembler-Programmier/in

## Sichtbarer Zustand

- Program Counter (PC): Aktuelle Stelle im Code

- Register (file): Werte zur direkten Bearbeitung, Funktionsparameter

- Condition Codes: Statusinformationen, Verzweigungen

#### Speicher

- Byte-adressierbares Array

- Programm- und Nutzdaten

- Stack: Funktionsaufrufe und lokale Variablen; per *Konvention* besonders ausgezeichneter Speicherbereich

(日)

## Instruktionssets

### ARM und x86: Unterschiedliche, inkompatible ISAs

- ▶ x86: CISC, vorwiegend Desktop und Cloud

- ARM: RISC, vorwiegend mobile Geräte (Handy, Tablet)

## Quellcode

```

int sum(int x, int y) {

int res;

res = x + y;

return (res);

}

```

イロト イポト イヨト イヨト 二日一

## Instruktionssets

ARM und x86: Unterschiedliche, inkompatible ISAs

- ▶ x86: CISC, vorwiegend Desktop und Cloud

- ARM: RISC, vorwiegend mobile Geräte (Handy, Tablet)

| ARM               | x86 (AT&T-Syntax)    |

|-------------------|----------------------|

| <pre>sum:</pre>   | <pre>sum:</pre>      |

| sub sp, sp, #20   | pushq %rbp           |

| str r0, [sp, #16] | movq %rsp, %rbp      |

| str r1, [sp, #12] | movl %edi, -20(%rbp) |

| ldr r2, [sp, #16] | movl %esi, -24(%rbp) |

| add r2, r2, r1    | movl -24(%rbp), %eax |

| str r2, [sp, #8]  | movl -20(%rbp), %edx |

| str r0, [sp, #4]  | addl %edx, %eax      |

| mov r0, r2        | movl %eax, -4(%rbp)  |

| str r1, [sp]      | movl -4(%rbp), %eax  |

| add sp, sp, #20   | popq %rbp            |

| bx lr             | ret                  |

## Instruktionssets

ARM und x86: Unterschiedliche, inkompatible ISAs

- ▶ x86: CISC, vorwiegend Desktop und Cloud

- ARM: RISC, vorwiegend mobile Geräte (Handy, Tablet)

| ARM               | x86 (Intel-Syntax)          |

|-------------------|-----------------------------|

| <pre>sum:</pre>   | <pre>sum:</pre>             |

| sub sp, sp, #20   | push rbp                    |

| str r0, [sp, #16] | mov rbp, rsp                |

| str r1, [sp, #12] | mov DWORD PTR [rbp-20], edi |

| ldr r2, [sp, #16] | mov DWORD PTR [rbp-24], esi |

| add r2, r2, r1    | mov eax, DWORD PTR [rbp-24] |

| str r2, [sp, #8]  | mov edx, DWORD PTR [rbp-20] |

| str r0, [sp, #4]  | add eax, edx                |

| mov r0, r2        | mov DWORD PTR [rbp-4], eax  |

| str r1, [sp]      | mov eax, DWORD PTR [rbp-4]  |

| add sp, sp, #20   | pop rbp                     |

| bx lr             | ret                         |

# Objektcode

#### ARM

| 0xe5 | 0x2d | 0xd0 | 0x04 | 0xe2 | 0x8d |

|------|------|------|------|------|------|

| 0xb0 | 0x00 | 0xe2 | 0x4d | 0xd0 | 0x14 |

| 0xe5 | 0x0b | 0x00 | 0x10 | 0xe5 | 0x0b |

| 0x10 | 0x14 | 0xe5 | 0x1b | 0x20 | 0x10 |

| 0xe5 | 0x1b | 0x30 | 0x14 | 0xe0 | 0x82 |

| 0x30 | 0x03 | 0xe5 | 0x0b | 0x30 | 0x08 |

| 0xe5 | 0x1b | 0x30 | 0x08 | 0xe1 | 0xa0 |

| 0x00 | 0x03 | 0xe2 | 0x8b | 0xd0 | 0x00 |

| 0xe8 | 0xbd | 0x08 | 0x00 | 0xe1 | 0x2f |

| 0xff | 0x1e |      |      |      |      |

#### Intel

| 0x55 | 0x48 | 0x89 | 0xe5 | 0x89 | 0x7d |

|------|------|------|------|------|------|

| 0xec | 0x89 | 0x75 | 0xe8 | 0x8b | 0x45 |

| 0xe8 | 0x8b | 0x55 | 0xec | 0x01 | 0xd0 |

| 0x89 | 0x45 | 0xfc | 0c8b | 0x45 | 0xfc |

| 0x5d | 0xc3 |      |      |      |      |

### Unterschiede und Ähnlichkeiten

- Beide Architekturen: Sequenz von Bytes (ARM umfangreicher!)

- Binärcode (offensichtlich) völlig unterschiedlich

- Grundlegende Prinzipien dennoch oft ähnlich

DatenverarbeituhgssyMaschine/CPU: Keine Kenntnissüber Hochsprachenquelltext!

#### ∽ Q (? 95 / 326

## Beispiel: Addition in Assembler I

| ARM-Assemblercode                                                                                            | C-Äquivalent                                                                                       |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| ldr r2, [fp, #-16]<br>ldr r3, [fp, #-20]<br>add r3, r2, r3<br>str r3, [fp, #-8]<br>Illustration: Siehe Tafel | <pre>int r2, r3, *fp; // Operanden aus Array // (Speicher) holen r2 = fp[-16]; r3 = fp[-20];</pre> |

|                                                                                                              | r2 = r2 + r3; // Addition                                                                          |

|                                                                                                              | <pre>// Resultat in Array schreiben fp[-8] = r2;</pre>                                             |

- Kurios: Array mit negativen Indizes

- Ansonsten: Sehr einfacher C-Code mit elementaren Operationen

## Beispiel: Addition in Assembler I

| x86-As     | semblercode                                          | C-Äquivalent                                                            |  |  |  |  |  |  |  |

|------------|------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| mov<br>mov | eax,DWORD PTR [rbp-0x18]<br>edx,DWORD PTR [rbp-0x14] |                                                                         |  |  |  |  |  |  |  |

| add        | eax,edx                                              | <pre>// Operanden aus Array // (Speicher) holen eax = rbp[-0x18];</pre> |  |  |  |  |  |  |  |

| mov        | DWORD PTR [rbp-0x4],eax                              | edx = rbp[-0x14];                                                       |  |  |  |  |  |  |  |

|            |                                                      | <pre>eax = eax + edx; // Addition</pre>                                 |  |  |  |  |  |  |  |

|            |                                                      | <pre>// Ergebnis in Array schreiben rbp[-0x4] = eax;</pre>              |  |  |  |  |  |  |  |

- Kurios: Array mit negativen Indizes

- Ansonsten: Sehr einfacher C-Code mit einfachsten Elementen

# Eigenschaften von Assembler I

#### Daten

- Daten: Eines oder mehrere Bytes

- Zeiger zur Speicheradressierung

- Datenverarbeitung in Registern (RISC) oder gemischt Register/Speicher (CISC)

- Speicher und Register untypisiert

- Keine zusammengesetzten Datentypen; kontinuierliche Speicherbereiche

#### Operationen

- ► Datentransfer Speicher ↔ Register

- Arithmetische und logische Funktionen auf Registern (CISC: auch Speicher) ausführen

- Programmfluss durch (bedingte) Sprünge und Unterroutinen

- CISC: Mächtige Spezialinstruktionen (AES, SHA, FFT, ...), RISC: Kombination elementarer Operationen

# Eigenschaften von Assembler II

### Stapelspeicher

- Jede Funktion: Arbeitsbereich auf Stack

- Lokale Variablen, Parameterübertragung (neben Registern, je nach Konvention – definiert in *ABI*-Dokument)

### Struktur

- Frame Pointer: Stapelanfang

- Stack Pointer: Aktuelles Stapelende

- Stack wächst von oben nach unten

- Daten auf Stack relativ zu FP oder SP adressierbar

### Vereinfachungen

- Funktionsaufrufe: Strukturen auf Stack komplexer

- Reale Speicheraufteilung deutlich komplizierter (Bibliotheken, Interaktionscode mit BS)

- cat /proc/(pid)/maps

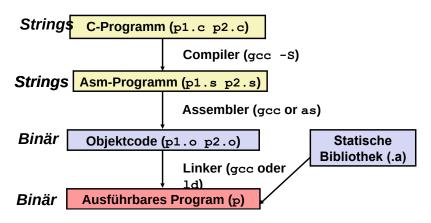

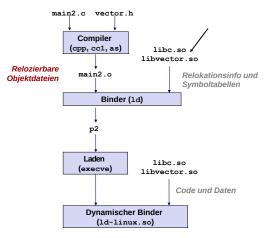

# Die Werkzeugkette I

#### Selbstverständnis Informatik

- Informatik ≠ Werkzeuge bedienen

- Aber: Ohne Werkzeuge kann man nichts erschaffen

- Verständnis: Prinzipien und Grundlagen

- Tun: Probleme der realen Welt lösen!

イロト イポト イヨト イヨト

# Die Werkzeugkette II

Abbildung basiert auf Bryant & O'Hallaron

# Die Werkzeugkette III

#### Werkzeuge (Tools)

- ▶ gcc: C-Compiler; Dispatcher für andere Teile der Kompilationskette

- ▶ gas: Assembler

- Id, Id. so: (Dynamischer und statischer) Binder/Linker

- objdump, readelf: Analyse (und Disassemblierung) von Binärdateien

- gdb: Debugger (Live- und Post-Mortem-Analyse)

- nm: Symbole anzeigen (Funktionen etc.)

- strings: Zeichenkettenkonstanten anzeigen

- addr2line: Adressen auf Quelltextsymbole abbilden

- Aus GNU Binutils: www.gnu.org/software/binutils

# Die Werkzeugkette IV

#### Anmerkungen

- (tool) für native Verwendung (host = target)

- Präfix für Cross-Tools (host ≠ target): arm-linux-gnueabi-(tool), mips-sgi-irix-(tool), ...

- Komplexität: gcc >1700, clang > 200 Kommandozeilenoptionen → mehr als (F5) drücken.

イロト イポト イヨト イヨト 二日

### Die Werkzeugkette V

```

sh> arm-linux-qnueabi-objdump -dS sum.o

int sum (int x, int y) {

0: e52db004 push {fp} ; (str fp, [sp, #-4]!)

4: e28db000 add fp, sp, #0

8: e24dd014 sub sp, sp, #20

c: e50b0010 str r0, [fp, #-16]

10: e50b1014 str r1, [fp, #-20]

int res;

res = x+v;

14: e51b2010 ldr r2, [fp, #-16]

18: e51b3014 ldr r3, [fp, #-20]

1c: e0823003 add r3, r2, r3

20: e50b3008 str r3, [fp, #-8]

return (res);

24: e51b3008 ldr r3, [fp, #-8]

28: e1a00003 mov r0, r3

2c: e28bd000 add sp, fp, #0

30: e8bd0800 ldmfd sp!, {fp}

34: e12fffle bx lr

(日)

```

### Die Werkzeugkette V

```

sh> objdump -dS sum.o

int sum (int x, int y) {

0: 55

push

rbp

1: 48 89 e5

rbp,rsp

mov

4: 89 7d ec

mov

DWORD PTR [rbp-0x14],edi

7:8975e8

DWORD PTR [rbp-0x18],esi

mov

int res;

res = x+y;

a: 8b 45 e8

eax, DWORD PTR [rbp-0x18]

mov

d: 8b 55 ec

edx, DWORD PTR [rbp-0x14]

mov

10: 01 d0

add

eax, edx

12: 89 45 fc

DWORD PTR [rbp-0x4], eax

mov

return (res);

15: 8b 45 fc

eax, DWORD PTR [rbp-0x4]

mov

18: 5d

rbp

pop

19: c3

ret.

```

3

# Die Werkzeugkette VI

#### gdb

- gdb (objekt): Funktioniert mit Binärdateien, Programmen, Core-Dumps

- Kann auch disassemblieren

- Statische Daten, aber auch laufende Programme analysieren und *manipulieren*

#### **Cross-Verwendung**

- Eingebettete Systeme, Tablets, Smartphones: Oft zu schwach/langsam, um darauf zu entwicklen

- Abbilfe: Cross-Debugging

- Gerät (Target): gdbserver

- Entwicklungsrechner (Host): gdb (mit minimalen Einschränkungen)

## Assembler: Struktur von Anweisungen I

#### Generelle Aufgaben

- Transfer Register  $\leftrightarrow$  Speicher

- Verknüpfen von (mehreren) Registern: Logisch, Arithmetisch

- Datenverarbeitung

- Kontrollfluss, Stack

- Systemkontrolle und -verwaltung

#### Komponenten

- Mnemonic gibt an, was gemacht werden soll

- ▶ 0-4 Argumente als Operanden

- Register: Wert direkt auslesen

- Speicher: Zugriff über Zeiger (aus Register)

- Unmittelbarer Wert (*Immediate*): Konstante in Anweisung einkodiert

- Weitere Spezialmöglichkeiten (Details später)

# Assembler: Struktur von Anweisungen II

### Allgemeine Struktur

- Häufig:  $\langle mnemonic \rangle \langle R_d \rangle$ ,  $Op_n$ ,  $Op_m$

- Reihenfolge: Ziel (destination), Argumente

- ▶ Bei Registern:  $n \in [0, 15]$ ;  $n \in [0, 12]$  frei verwendbar

### Beispiel: Speicher/Register-Transfer

- Format:  $\langle mnemonic \rangle \langle R_d \rangle \langle R_n \rangle$

- ldr r0, [r1]

- Idr = Load RegisteR

- ▶ Transfer Speicher  $\rightarrow$  Register

- $\land \langle \mathbf{R}_{o} \rangle \leftarrow \operatorname{memory}[\langle \mathbf{R}_{i} \rangle]$

- [r1]: Dereferenzierung

- Nebenbedingung: Ausrichtung der Daten an 32-Bit-Grenzen!

- Adresse Vielfaches von 4 Bytes: 0, 4, 8, 12, ...

ARM (RISC): Kein Transfer Speicher ↔ Speicher

# Assembler: Struktur von Anweisungen II

### Allgemeine Struktur

- Häufig:  $\langle mnemonic \rangle \langle R_d \rangle$ ,  $Op_n$ ,  $Op_m$

- ▶ Reihenfolge: Ziel (*destination*), Argumente

- ▶ Bei Registern:  $n \in [0, 15]$ ;  $n \in [0, 12]$  frei verwendbar

### Beispiel: Speicher/Register-Transfer

- Format:  $\langle mnemonic \rangle \langle R_d \rangle \langle R_n \rangle$

- str r0, [r1, #N]

- str = Store RegisteR

- #N: Additive Konstante (Angabe generell möglich)

- ▶ Transfer Register  $\rightarrow$  Speicher

- $\langle \mathbf{R}_{\mathbf{o}} \rangle \to \operatorname{memory}[\langle \mathbf{R}_{\mathbf{i}} \rangle + N]$

- Gleiche Alignment-Anforderungen

- ► ARM (RISC): Kein Transfer Speicher ↔ Speicher

### Struktur von Assembler-Anweisungen III

| Variablen vertauschen                                                                                      | Assembler-Code                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| <pre>void swap(int *xp, int *yp) {     int t0 = *xp;     int t1 = *yp;     *xp = t1;     *yp = t0; }</pre> | <pre>ldr r3, [fp, #-16] int t0 = *xp<br/>ldr r3, [r3]<br/>str r3, [fp, #-12]<br/>ldr r3, [fp, #-20] int t1 = *yp<br/>ldr r3, [r3]<br/>str r3, [fp, #-8]</pre> |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                            | <pre>ldr r3, [fp, #-16] *xp = t1;<br/>ldr r2, [fp, #-8]<br/>str r2, [r3]</pre>                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                            | ldr r3, [fp, #-20] *yp = t0;<br>ldr r2, [fp, #-12]<br>str r2, [r3]                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

### Illustration: Siehe Tafel

イロト イポト イモト イモト 一日

# Inhalt

#### Überblick und Einführung Literatur Lernziele

#### Datenrepräsentation und -manipulation

Zahlendarstellung Endianess Zeichendarstellung Gleitkommazahlen Bitoperationen

#### Prozessorarchitektur

Grundkoperationen einer CPU von Neumann- und Harvard-Architektur Grundkonzept der Befehlsausführung Befehlszyklen und Pipelines Optimierungsmechanismen Sonstige Themen

#### Hochsprachen und Assembler I

Instruktionssets Die Werkzeugkette

#### ARM-Assembler

ARM-CPU-Architektur ARM-Assemblerprogrammierung Befehlsgruppen Schleraufbau ibliotheken, Binden & ELF-Binärformat Grundlagen Bibliotheken Bibliotheken Gotaprachen & Compiler Aufgaben und Überblick Syntaxanalyse Semantische Analyse & Codegenerierun Optimierungen

#### Speicherhierarchie, Caches und MMUs

RAM-Speicher Festplatten und Massenspeichergeräte CPU-Speicher-Kluft und Lokalität Caches Caches-Optimierungen Virtueller Speicher und Memory Management Units

#### Betriebssysteme

Grundstruktur Memory Management Unit und Adressrauwnerwaltung Interrupts Ausprägungen von BS Fallbeispiel: Linux Blockgeräte und Dateisysteme

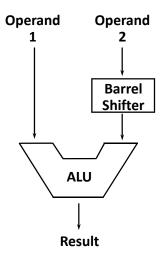

# **ARM-Architektur I**

#### Grundzüge der ARM-Architektur

- ► Alle Instruktionen: 32 Bit-Kodierung

- ▶ Fast alle Befehle in einem Zyklus ausführbar

- RISC »ohne religiösen Eifer«

- Viele Befehle bedingt ausführbar

- Load/Store-Architektur

- Operationen ausschließlich auf Registern

- ISA über Koprozessoren erweiterbar

- Systemverwaltung (System Control)

- Gleitkommaeinheit (Floating Point)

- Multimedia

٠..

イロト 不得 トイラト イラト 二日

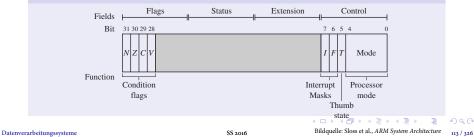

## **ARM-Architektur II**

#### Registersatz

- ▶ 16 Register (im Userland) sichtbar

- $(R_0) \dots \langle R_{12} \rangle$  frei verwendbar

- (R<sub>13</sub>): Stack Pointer, SP

- $(R_{14})$ : Link Register, LR (für Prozeduraufrufe)

- $\land$   $\langle R_{15} \rangle$ : Program Counter, PC (aktuelle Stelle im Code + 8 Bytes)

- Spezialregister: CPSR (Current Program Status Register)

- Steuert bedingte Operationen

- Über Spezialbefehle ansprechbar

# ARM-Architektur III

(Normative) Informationsquellen

- ► ISA: ARM Architecture Reference Manual (ARM ARM)

- Definiert allgemeine Architektur

- Keine implementierungsspezifischen Details (aber: generelle Grenzen)

- ▶ Implementierung: ARM Technical Reference Manual (ARM TRM)

- Spezifisch f

ür eine Implementierungsvariante

- Generische ISA von allen Implementierungen umgesetzt

- Alle Dokumente verfügbar auf http://infocenter.arm.com

#### **Details! Details! Details!**

Viele Details! 🖙 Manche Details (vorerst) ignorieren

イロト 不得 トイラト イラト 二日

# ARM-Architektur III

(Normative) Informationsquellen

- ► ISA: ARM Architecture Reference Manual (ARM ARM)

- Definiert allgemeine Architektur

- Keine implementierungsspezifischen Details (aber: generelle Grenzen)

- ▶ Implementierung: ARM Technical Reference Manual (ARM TRM)

- Spezifisch f

ür eine Implementierungsvariante

- Generische ISA von allen Implementierungen umgesetzt

- Alle Dokumente verfügbar auf http://infocenter.arm.com

#### Details! Details! Details!

Viele Details! 🖙 Manche Details (vorerst) ignorieren

イロト 不得 トイラト イラト 二日

# Registeraufbau und CPU-Architektur I

Register

- $\langle R_{0} \rangle \langle R_{12} \rangle (\langle R_{13} \rangle)$ : Orthogonal

- Zugriff auf CPSR aus User-Mode nur lesend

#### Status-Register: Details

### **CPU-Architektur II: Datenfluss**

#### Reale Welt...

- Komplexer

- Abhängig von HW-Implementierung

- Semantik immer identisch!

イロト イ理ト イヨト イヨト

3

ARM-Assemblerprogrammierung

# Inline-Assembler I

#### gcc: Inline-Assembler

```

void test_asm() {

// Effektives nop

asm("mov r3, r3")

}

```

#### **Caveat Emptor**

Low-Level-»Optimierungen« typischerweise schlechter als generierter Code!

#### Rationale

- Einfache Test/Experimentiermöglichkeit

- Reale Welt: Funktionen ohne Hochsprachen-Unterstützung (alternativ: Compiler-Intrinsics)

- Reine Assembler-Programme (natürlich) möglich

イロト 不得 トイラト イラト 二日

## Inline-Assembler II

#### **Allgemeine Syntax**

- > asm((code) : (Liste Ausgabeoperanden) : (Liste Eingabeoperanden) : (Clobber-Liste));

- to clobber = verprügeln; d.h. Modifikation eines Registers

```

int main() {

uint32_t result;

uint32_t value = 0x8;

printf("Wert vor asm: 0x%x\n", value); // 0x8 = 1000b

asm("mov %0, %1, ror #1" : "=r" (result) : "r" (value));

printf("Wert nach asm: 0x%x\n", result); // 0x4 = 0100b

return(0);

}

Details Inline-Assembler: Siehe gcc-Dokumentation

```

▲□▶▲□▶▲□▶▲□▶ □ のの⊙

ARM-Assemblerprogrammierung

## Standalone-Assembler I

#### Beispiel: Eigenständiges Assembler-Programm

```

/* Eigenständiges Assembler-Programm */

.global main /* main: Haupteintrittspunkt als globales Symbol */

.func main /* main als Funktion kenntlich machen */

main: /* Label für main*/

mov r0, #42 /* r0: Per Konvention BS-Returncode */

bx lr /* Rücksprung */

.endfunc

```

#### HOWTO

- In Binärobjekt verwandeln (assemblieren): arm-linux-gnueabi-as standalone.s -o standalone.o

- Linken (in ausführbares Programm verwandeln): arm-linux-gnueabi-gcc standalone.o -o standalone

DatenverarbeituhgssyAbkürzung: arm-linux-gnueabi-gcc standalone.s -o

```

うへで

117/326

```

L\_ARM-Assemblerprogrammierung

### Standalone-Assembler II

- Returncode ausgeben: ./standalone; echo \$?

- file: Unterschiedliche Binärobjekte

- nm: Unterschiedliche Symbole

Demo: Siehe Rechner

イロト イポト イヨト イヨト 二日

ARM-Assemblerprogrammierung

# Standalone-Assembler II

#### Assembler-Syntax

- directive (arguments): Meta-Anweisungen an den Assembler

- label: Funktionsnamen, Sprungziele

- #(Zahl): Unmittelbarer Wert (Immediate)

#### Assembler-Syntax II

- Kommentarzeilen

- Comment

- C-Kommentare

- Kommentare extrem wichtig!

- Syntaktischer Zucker, Makros, etc: Siehe gas-Anleitung

イロト イポト イヨト イヨト 二日

ARM-Assemblerprogrammierung

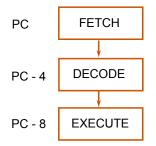

# Pipelining

#### **Pipeline-Verarbeitung**

- Instruktionen in mehreren Phasen ausgeführt

- Original-Pipeline: 3 Stufen

- 1. Instruktion aus Speicher lesen

- 2. Dekodieren verwendeter Register

- Register lesen, Operation ausführen, Register zurückschreiben

- Neuere CPUs: Längere Pipelines

- Struktur Teil der ISA

#### Konsequenz

- PC-»Versatz« um 8 Bytes

- Dumps, Relokation (siehe später) etc. zu berücksichtigen

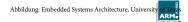

Abbildung: Embedded Systems Architecture, University of Texas

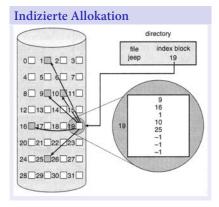

# Überblick: Instruktionsformat I

| 3 3 2 2<br>1 0 9 8 | 2<br>7 | 2<br>6 | 2<br>5 | 2<br>4 | 2<br>3 | 2<br>2     | 2<br>1 | 2<br>0 | 1 1 1<br>9 8 7 | 1<br>6 | 1<br>5 | 1<br>4        | 1<br>3 | 1<br>2 | 1<br>1   | 1<br>0 | 9     | 8 | 7                  | 6                   | 5   | 4  | 3 2 1 0                   | Instruction Type          |

|--------------------|--------|--------|--------|--------|--------|------------|--------|--------|----------------|--------|--------|---------------|--------|--------|----------|--------|-------|---|--------------------|---------------------|-----|----|---------------------------|---------------------------|

| Condition          | 0      | 0      | Т      |        | OPC    | ODE        | Ξ      | s      | Rn             |        |        | Rs            |        |        |          |        |       | 0 | PER                | AND                 | -2  |    | Data processing           |                           |

| Condition          | 0      | 0      | 0      | 0      | 0      | 0          | А      | s      | Rd             |        | Rn     |               |        |        | Rs       |        |       |   | 1                  | 0                   | 0   | 1  | Rm                        | Multiply                  |

| Condition          | 0      | 0      | 0      | 0      | 1      | U          | А      | s      | Rd HIGH        | ł      | I      | Rd LOW        |        |        | Rs       |        |       | 1 | 0                  | 0                   | 1   | Rm | Long Multiply             |                           |

| Condition          | 0      | 0      | 0      | 1      | 0      | в          | 0      | 0      | Rn             |        | Rd     |               | ł      |        | 0        | 0      | 0     | 0 | 1                  | 0                   | 0   | 1  | Rm                        | Swap                      |

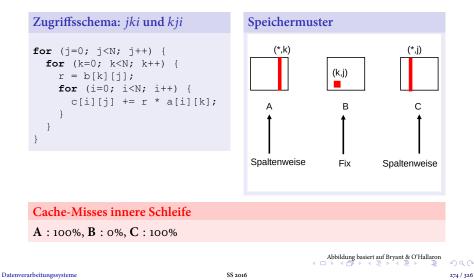

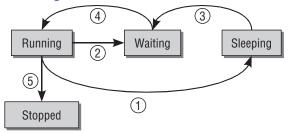

| Condition          | 0      | 1      | Т      | Ρ      | U      | в          | w      | L      | Rn             |        |        | Ro            | ł      |        | OFFSET   |        |       |   |                    |                     |     |    |                           | Load/Store - Byte/Word    |